Université Mohammed V de Rabat

Faculté des sciences

SMI Semestre 3

Module: Electronique

# TP 3: Opérations arithmétiques et drapeaux d'état

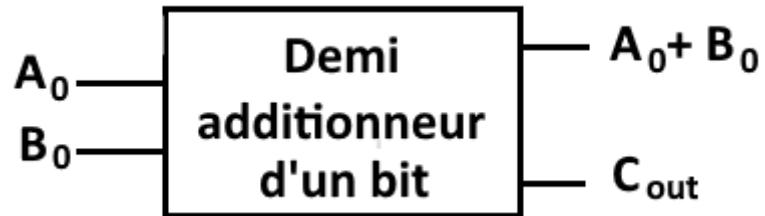

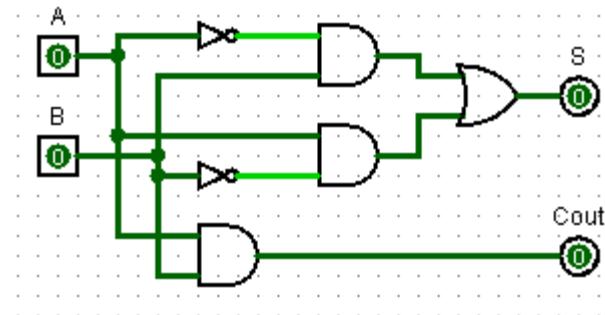

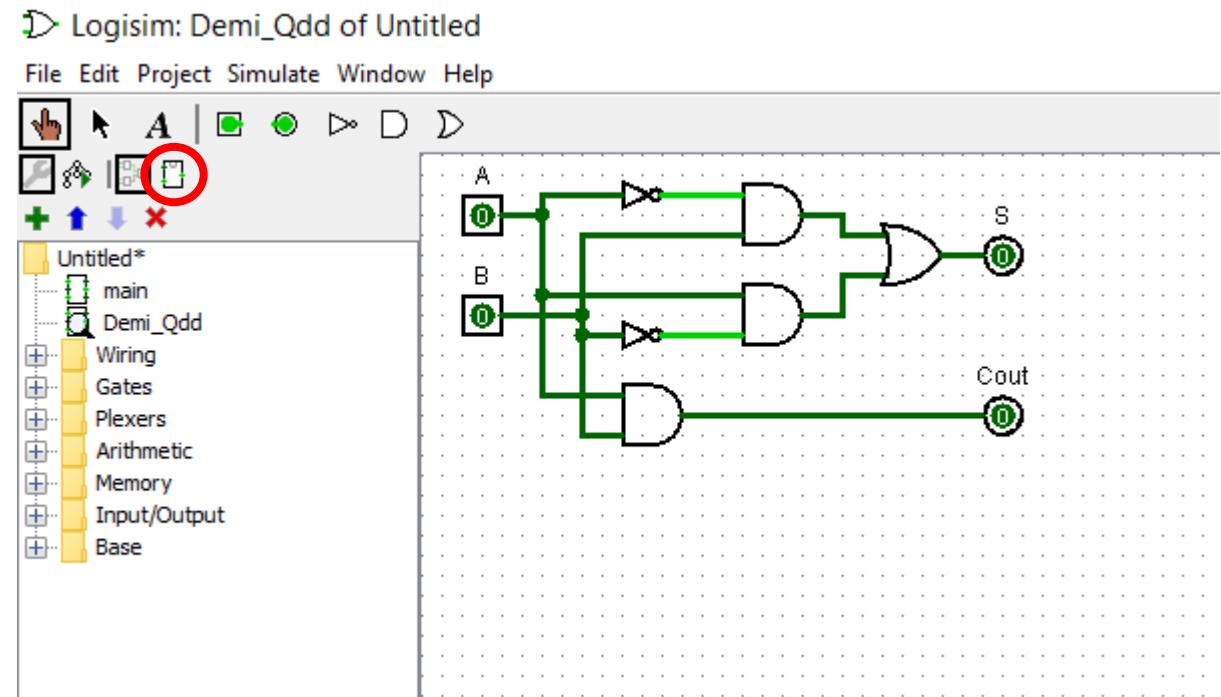

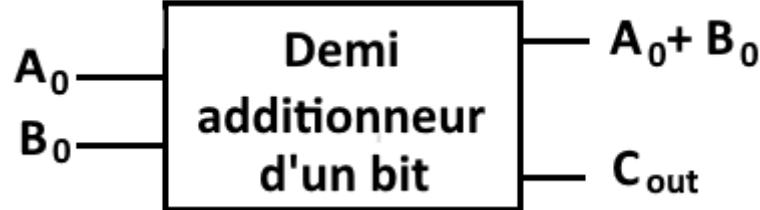

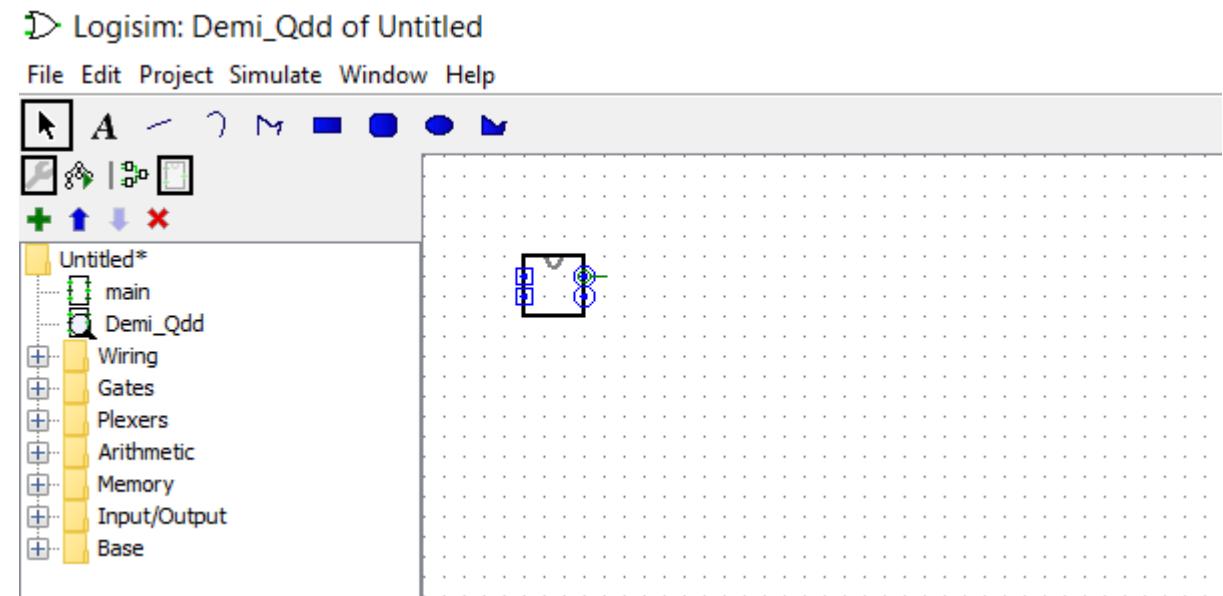

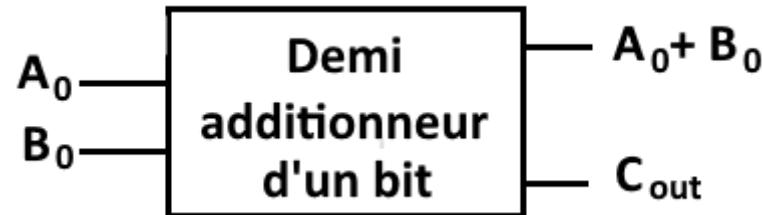

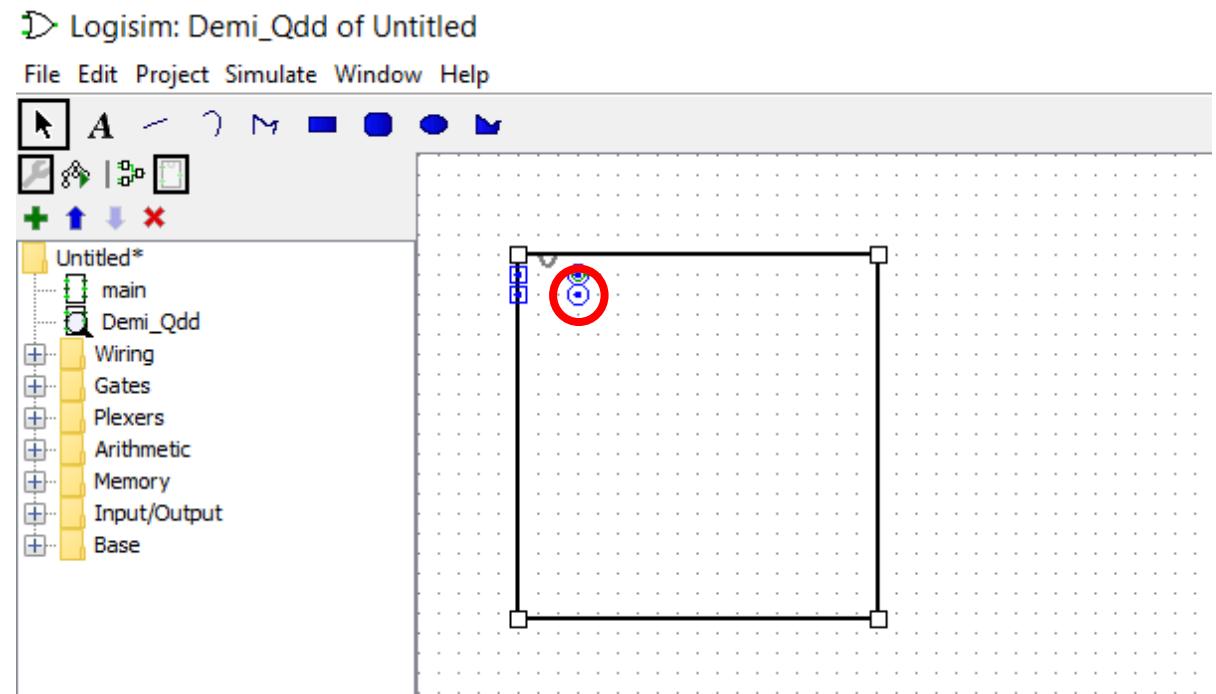

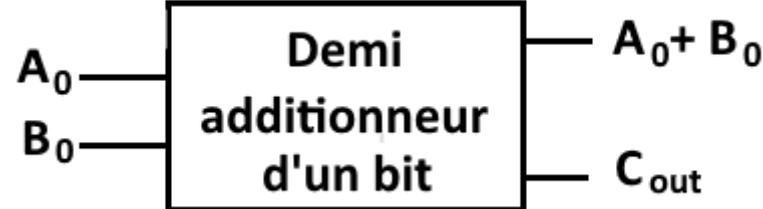

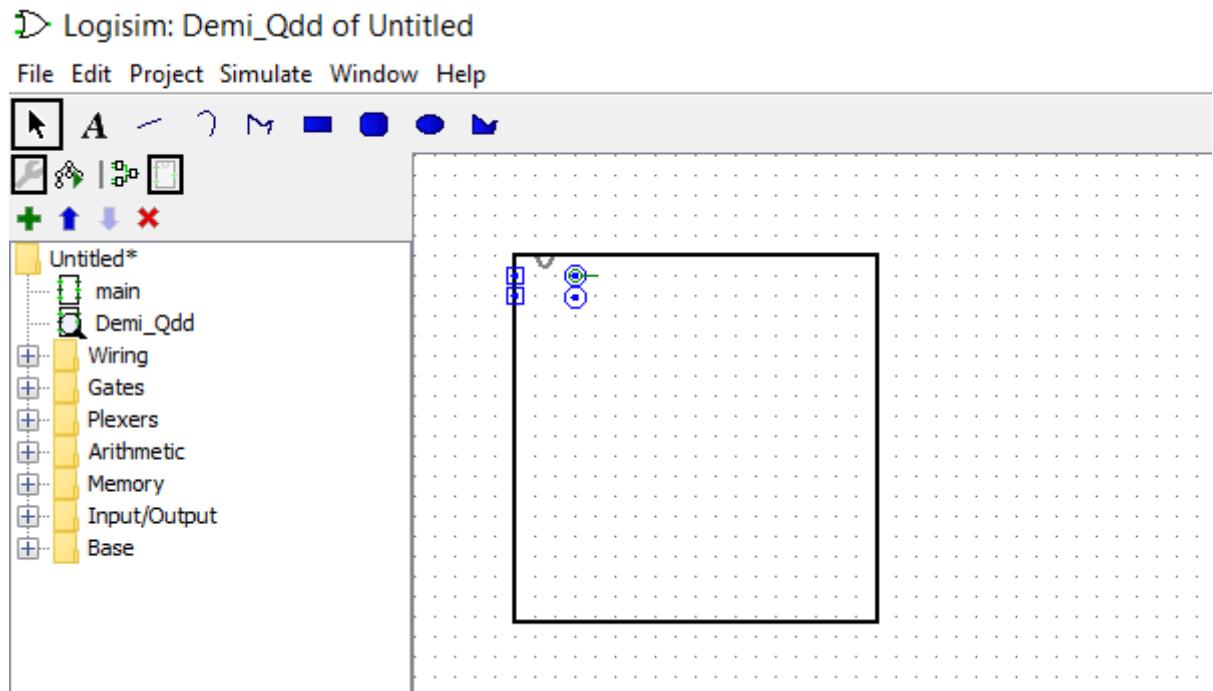

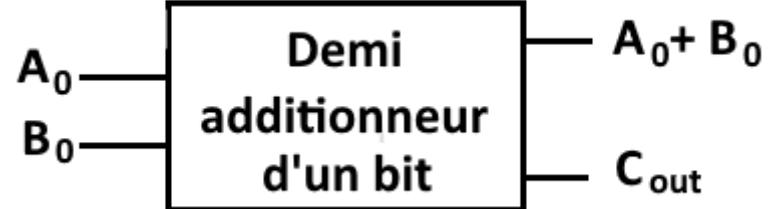

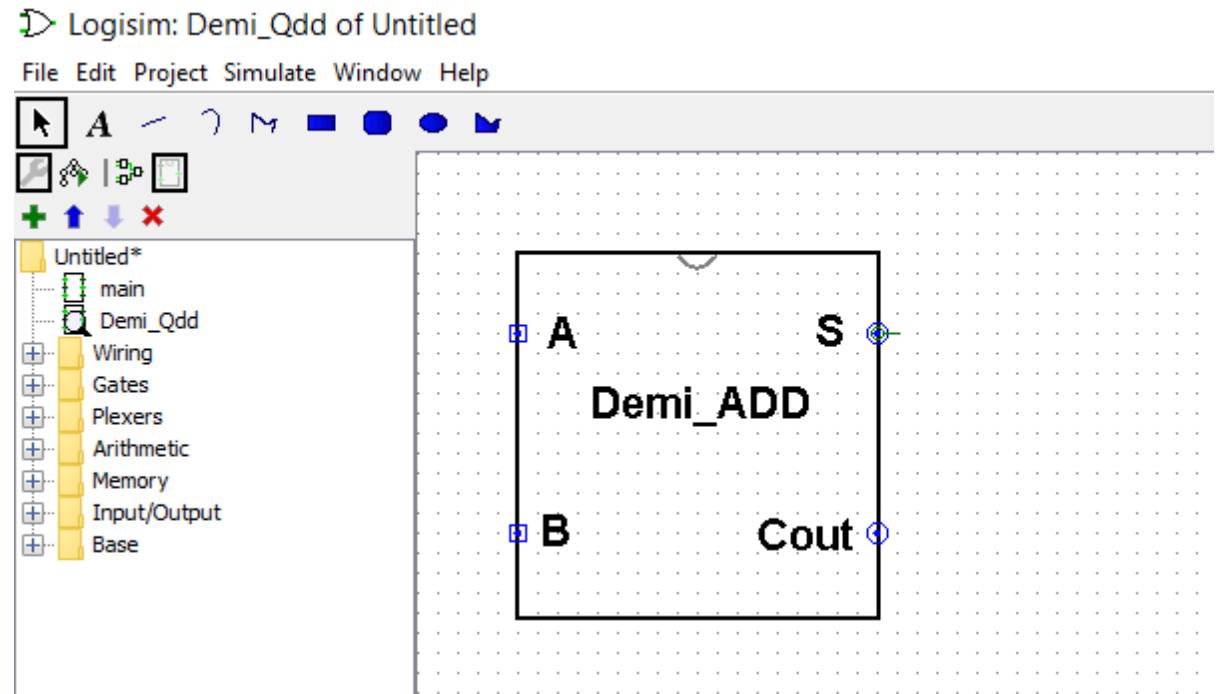

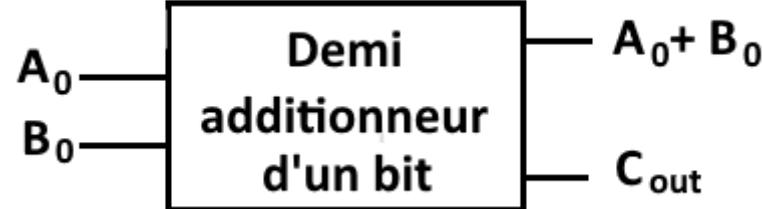

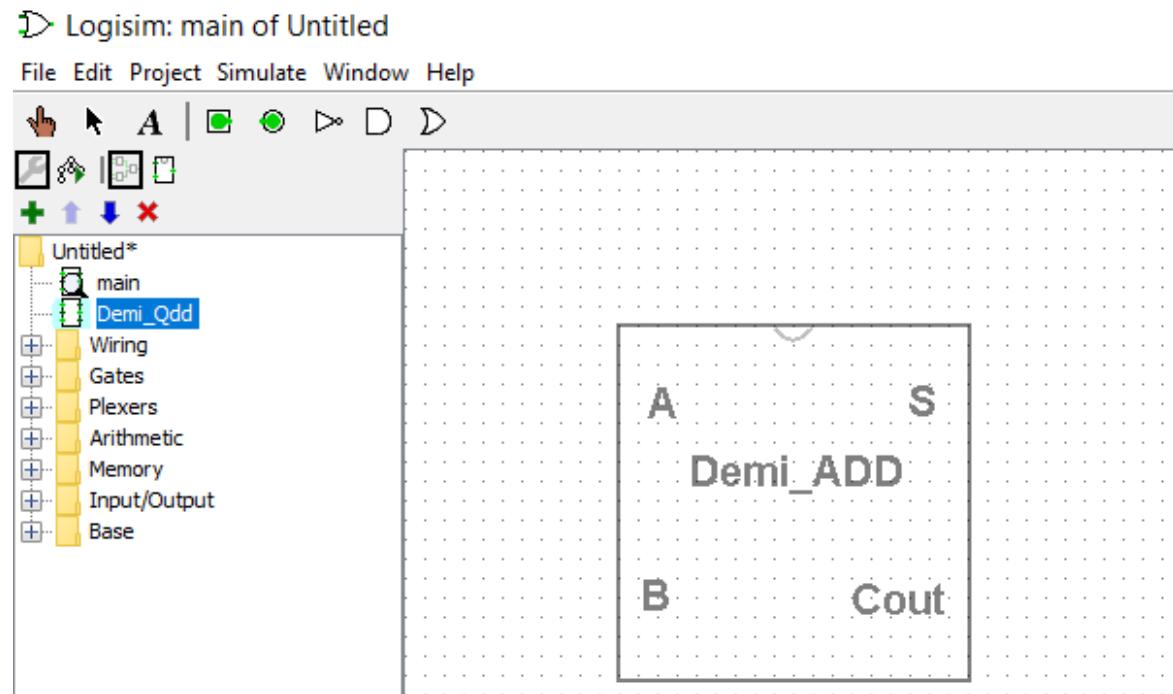

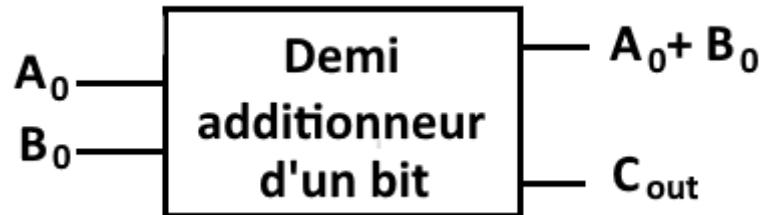

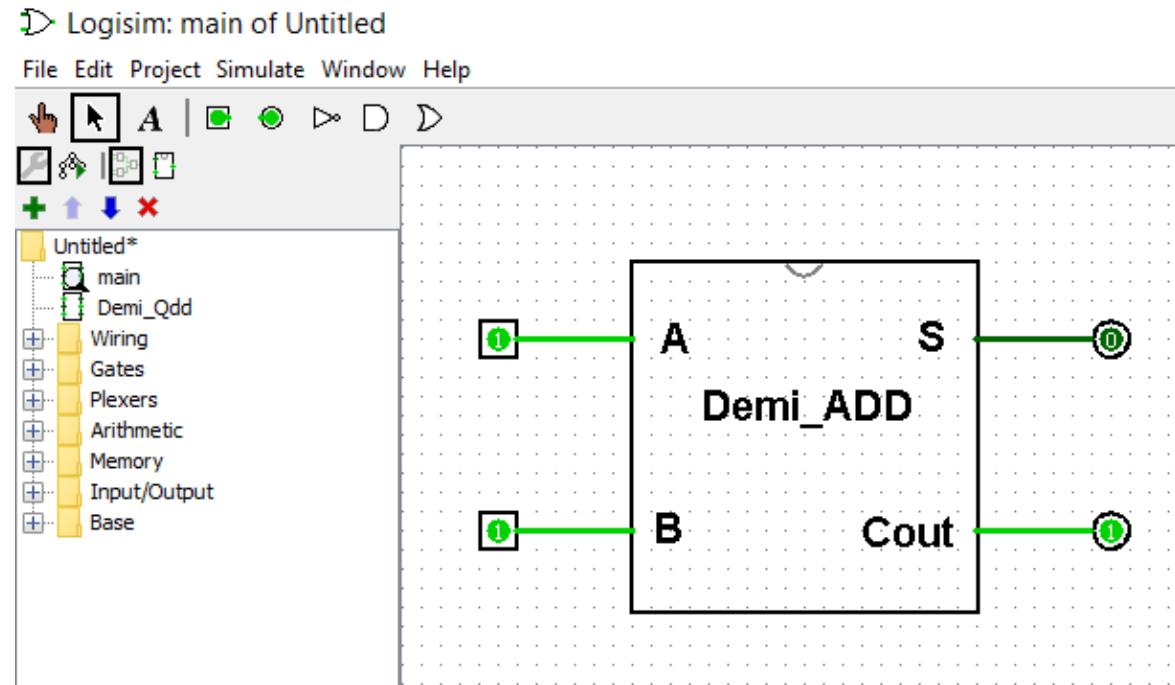

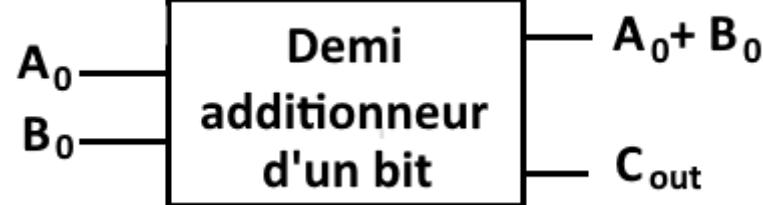

# 1. Demi-additionneur d'un bit

| A | B | S | Cout |

|---|---|---|------|

| 0 | 0 | 0 | 0    |

| 0 | 1 | 1 | 0    |

| 1 | 0 | 1 | 0    |

| 1 | 1 | 0 | 1    |

# 1. Demi-additionneur d'un bit

# 1. Demi-additionneur d'un bit

# 1. Demi-additionneur d'un bit

# 1. Demi-additionneur d'un bit

# 1. Demi-additionneur d'un bit

# 1. Demi-additionneur d'un bit

# 1. Demi-additionneur d'un bit

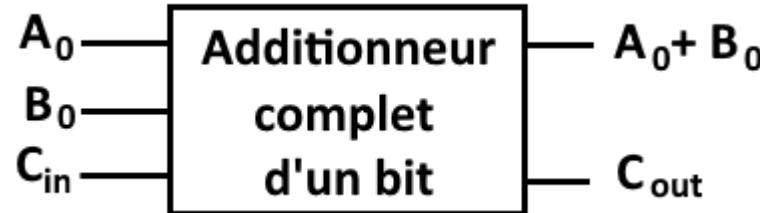

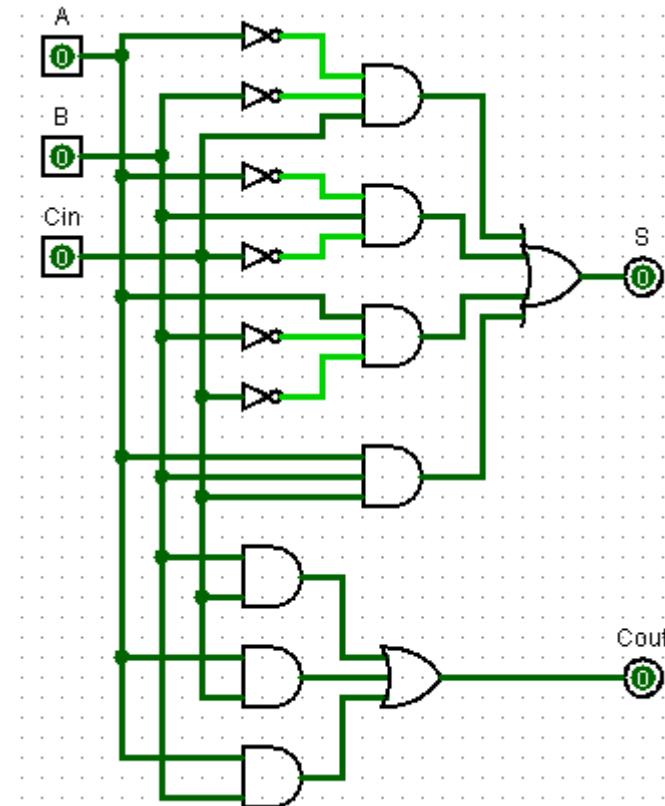

## 2. Additionneur complet d'un bit

| A | B | Cin | S | Cout |

|---|---|-----|---|------|

| 0 | 0 | 0   | 0 | 0    |

| 0 | 0 | 1   | 1 | 0    |

| 0 | 1 | 0   | 1 | 0    |

| 0 | 1 | 1   | 0 | 1    |

| 1 | 0 | 0   | 1 | 0    |

| 1 | 0 | 1   | 0 | 1    |

| 1 | 1 | 0   | 0 | 1    |

| 1 | 1 | 1   | 1 | 1    |

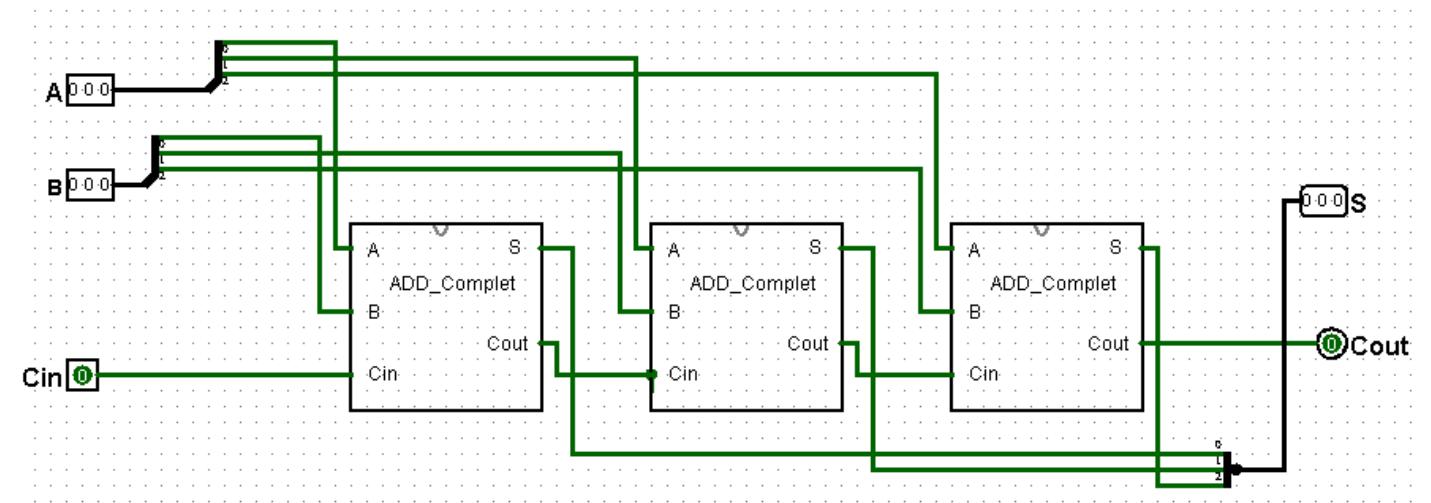

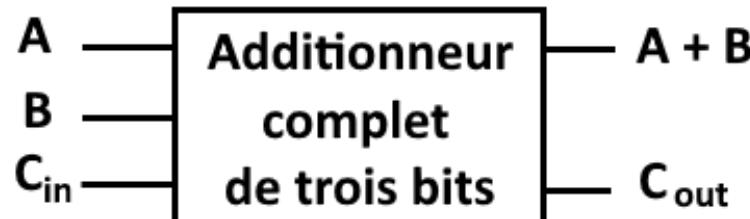

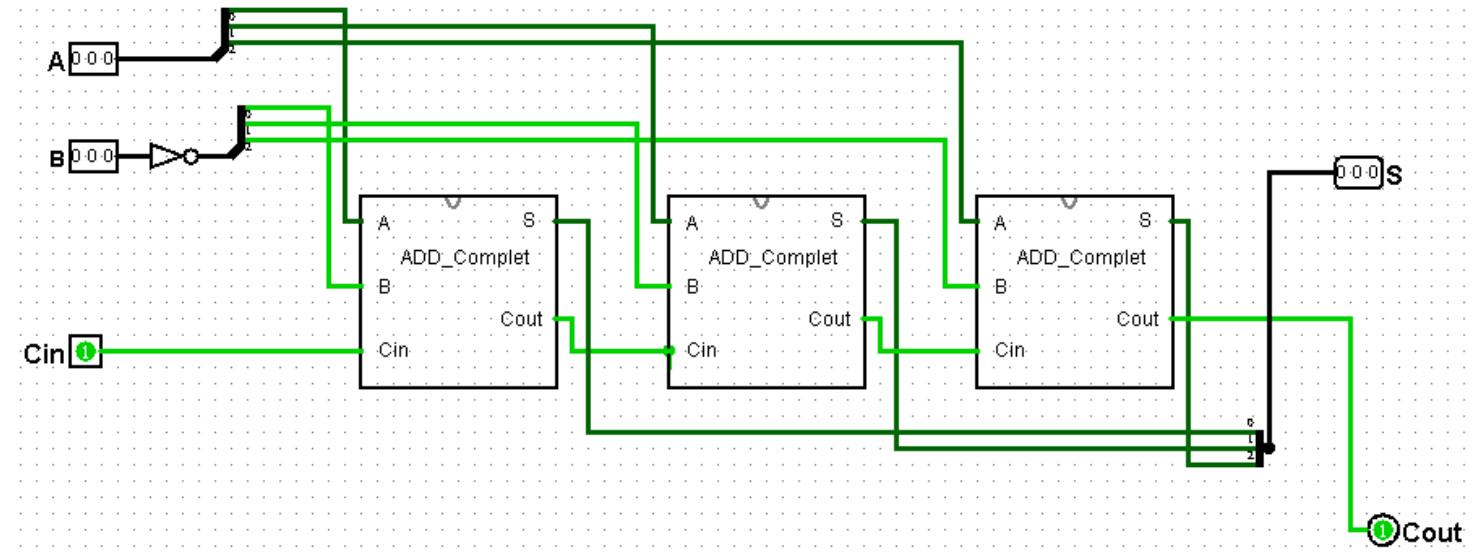

### 3. Additionneur complet de 3 bits

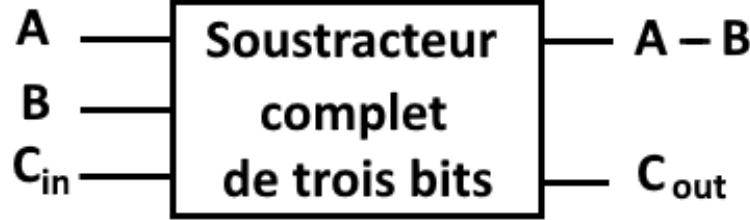

## 4. Soustracteur de 3 bits

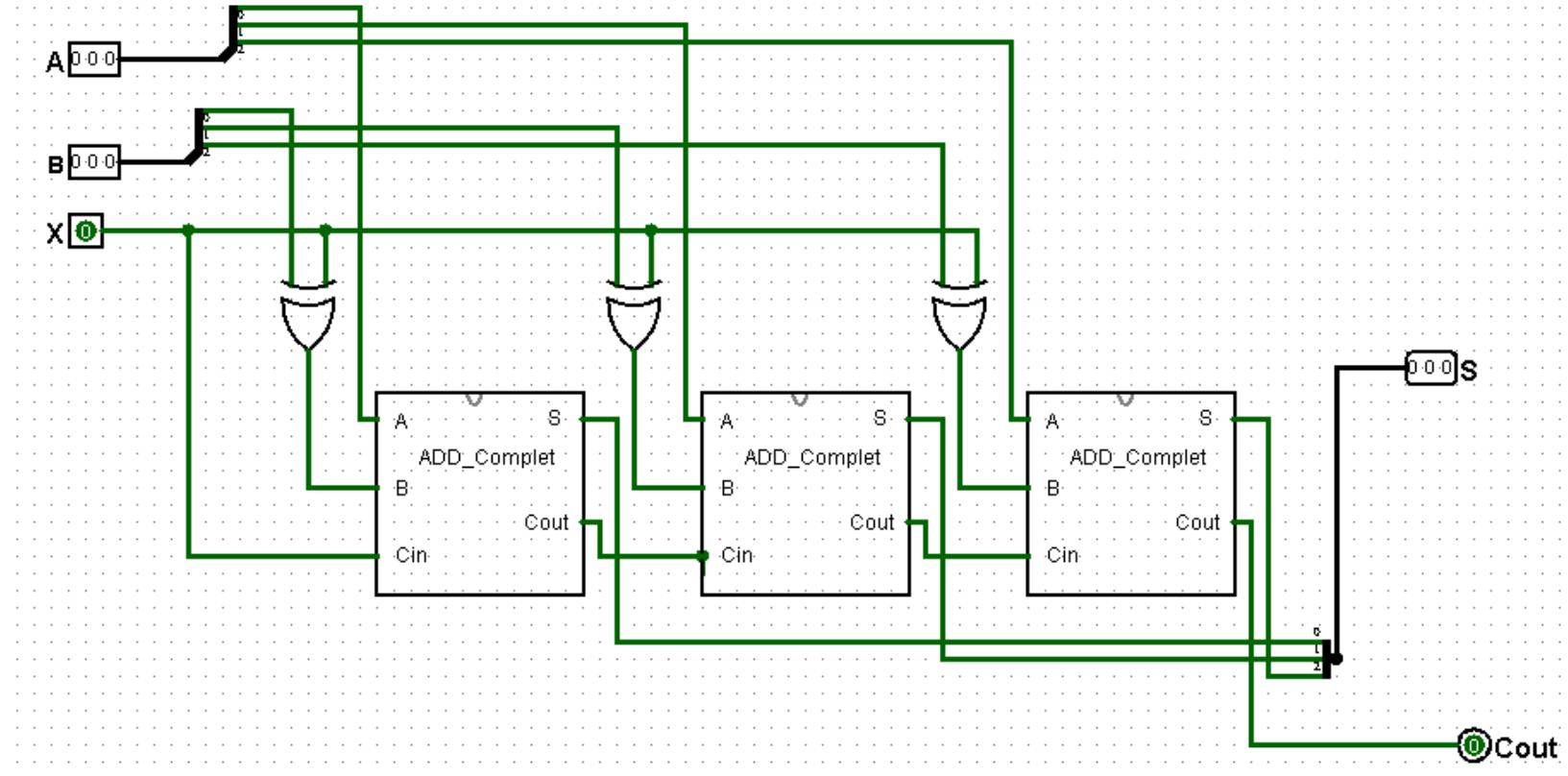

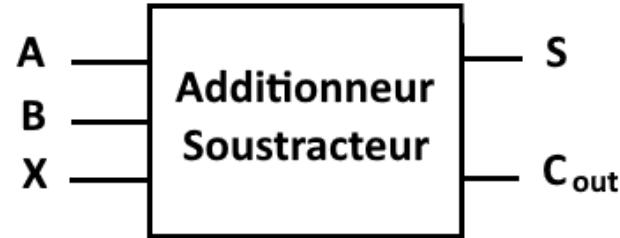

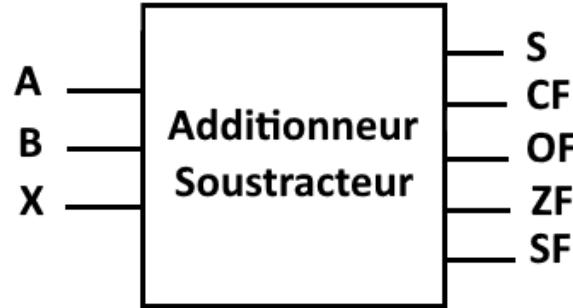

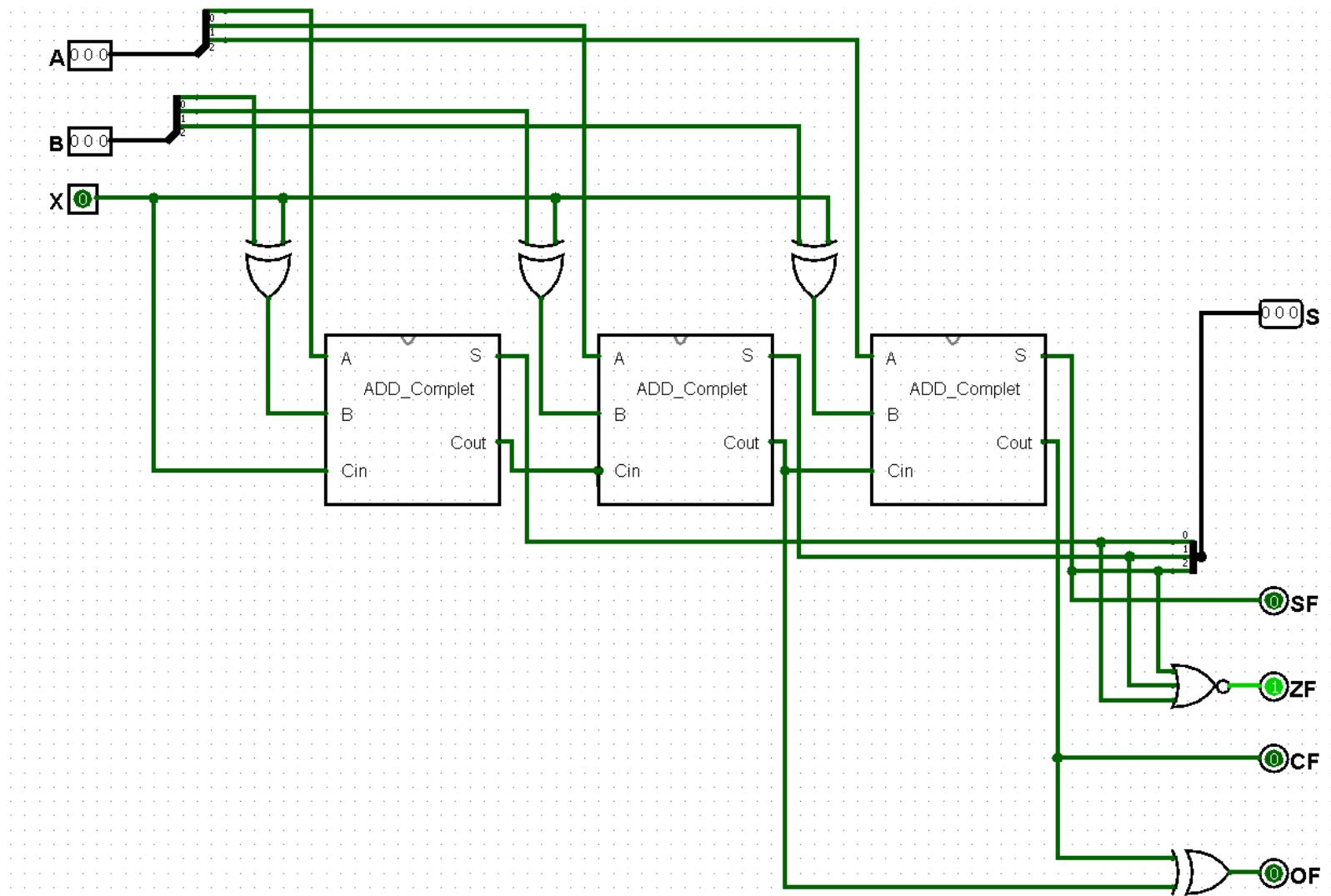

## 5. Additionneur/Soustracteur 3 bits

## 6. Additionneur/Soustracteur 3 bits et flags d'états

$$SF = S_{n-1}$$

$$CF = Cout_{n-1}$$

$$OF = Cin_{n-1} \oplus Cout_{n-1}$$

$$ZF = \overline{S_0 + S_1 + S_2}$$

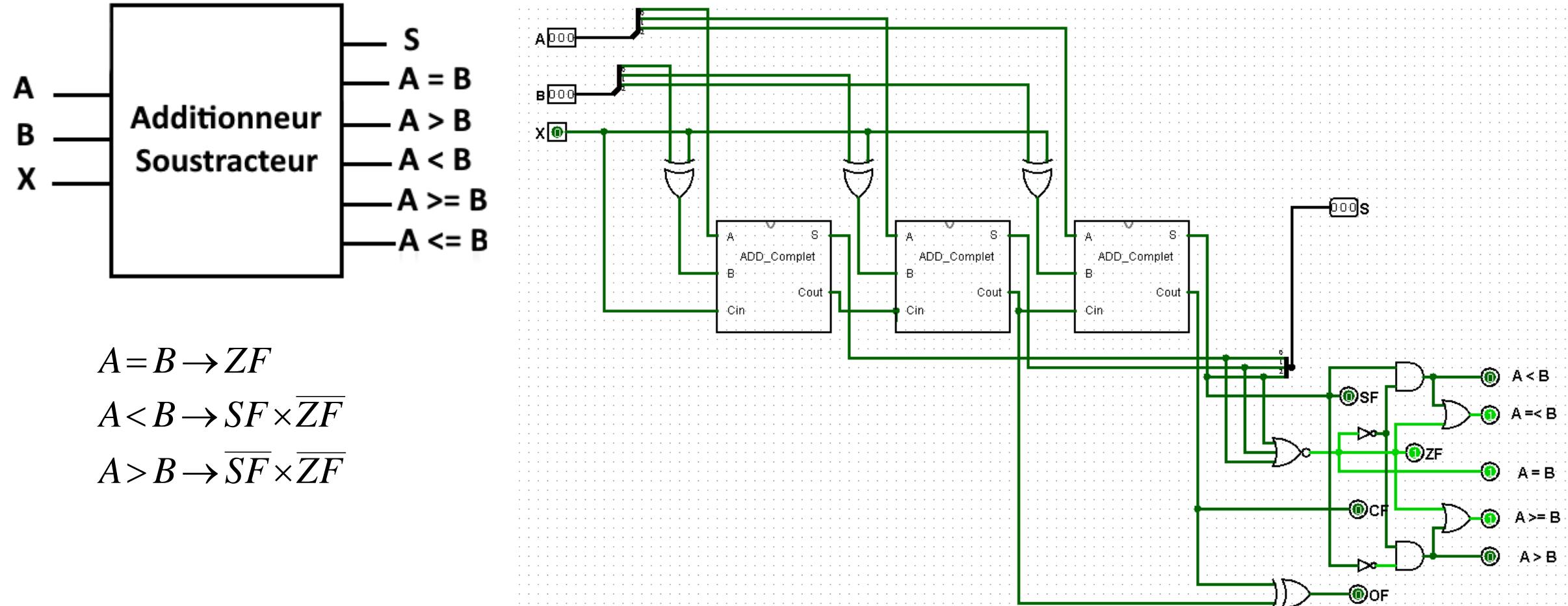

## 7. Additionneur/Soustracteur 3 bits et les opérations de comparaison

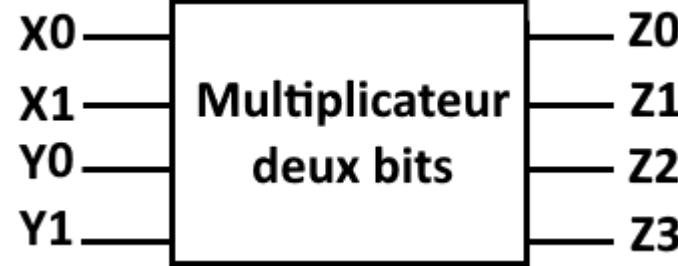

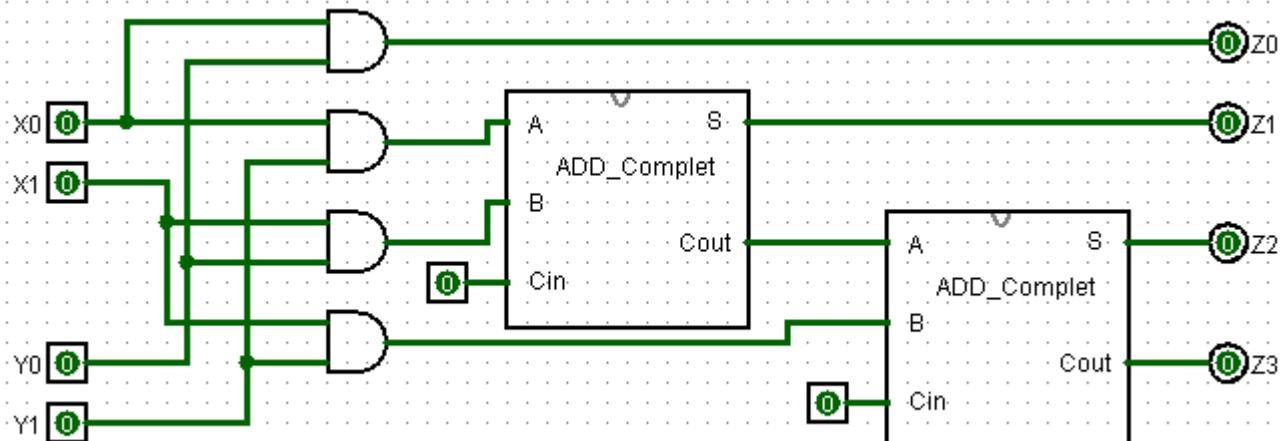

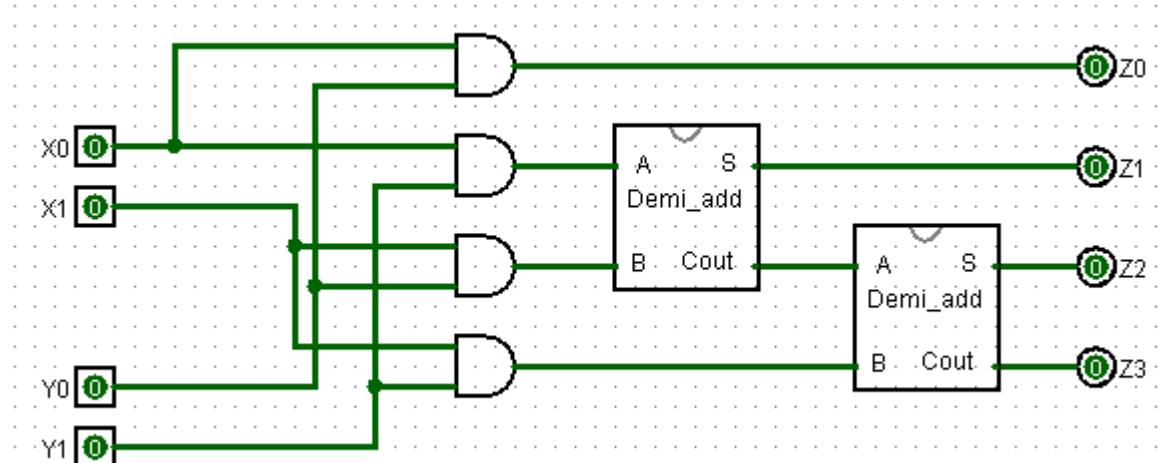

## 8. Multiplicateur de 2 bits

$$Z_0 = X_0 Y_0$$

$$Z_1 = X_0 Y_1 + X_1 Y_0 = A + B$$

$$Z_2 = X_1 Y_1 + Cout_1$$

$$Z_3 = Cout_2$$

A la séance prochaine